Lenovo

# High-Performance Infrastructure to Power Growing Electronic Design Automation (EDA) Simulation Article

For several decades, semiconductor design and manufacturing companies have been using EDA tools to:

- Design and validate the manufacturing process to ensure it delivers semiconductor chips with the required performance, density, quality, and yields.

- Verify that a chip design meets functionality, reliability, and performance requirements.

- Monitor the performance throughout the silicon lifecycle from post-manufacturing test to field deployment and operation.

EDA workloads consist of two high-level design phases (Figure 1) with a mix of sequential and threaded codes that are highly compute-intensive. The Front-End Design phase mainly has small files, which are more dominant. The Back-End phase typically has large files. Verification and regression usually consume most of the computing capacity.

| Front-End Design                               |                                                                             |                                                                                 | Back-End Design                                                                            |                                                                |                                                                                                                                                   | Manufacturing                                                                                    |

|------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Design<br>Specification                        | Verification/<br>Regression                                                 | Logic/Physical<br>Synthesis                                                     | Physical<br>Design                                                                         | Physical<br>Verification                                       | Timing/SI/Power<br>Signoff                                                                                                                        | Tape-out<br>Release to Fab                                                                       |

| Design entry<br>(HDL or Tran-<br>sistor level) | Simulation<br>• RTL/transistor<br>• Gate Level<br>• Formal/equiv-<br>alency | Logic to Gates<br>Mapping<br>• Start convert-<br>ing code to<br>actual circuits | Physical<br>Implementation<br>• Floor planning<br>and block/cell<br>placement<br>• Routing | DRC     LVS     ERC     Yeild checks     and enhance-     ment | <ul> <li>Parasitic Ex-<br/>traction</li> <li>Timing</li> <li>Noise/Signal In-<br/>tegrity</li> <li>Power analysis<br/>(static/dynamic)</li> </ul> | Released to<br>foundry/fab<br>• OPC<br>• MDP<br>• DRC/LVS<br>• Yield analysis and<br>enhancement |

Figure 1. The EDA Workflow

Today's semiconductor chips are incredibly complex and can contain over one billion circuit elements, all interacting with each other in subtle ways and highly sensitive to minor variations in the manufacturing process. Projects must be error-free before tape-out to mitigate the high costs of committing a design to silicon.

To manage this level of complexity, sophisticated automation with EDA on a high-performance infrastructure is critical for:

- **Faster Time-to-Market:** Accelerate complex EDA tasks, such as simulation, verification, and synthesis, to iterate through design cycles quicker, ultimately reducing time-to-market for new products and gaining competitive advantage.

- Innovative Design Exploration and Optimization: Explore a broader range of design options and parameters, leading to the discovery of improved and optimized product designs.

- Handling Larger Designs: Work on advanced technologies and more intricate integrated circuits.

- **Parallel Processing for Efficiency:** Designers can parallelize many EDA tasks to take advantage of large core counts that significantly improve efficiency and computational throughput.

• Improved Simulation Accuracy: More detailed and precise simulations are crucial for ensuring the reliability and performance of semiconductor devices.

Consequently, the use of EDA in semiconductor manufacturing can be essential.

## **EDA Benefits Beyond the Electronics Industry**

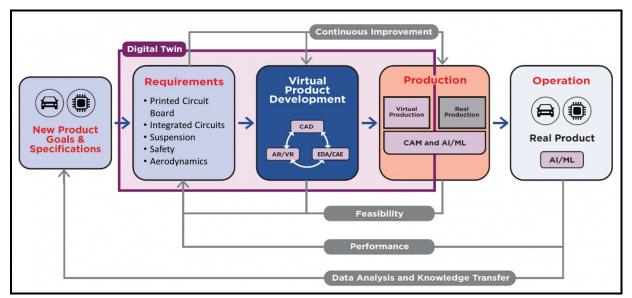

However, EDA use is not just confined to the electronics industry. Semiconductor chips and systems are significant components of autos, aircraft, and medical devices. The modern car is essentially a computer on wheels. It is designed and developed with many computer-aided design/engineering (CAD/CAE), EDA, augmented/virtual reality (AR/VR), and artificial intelligence/machine learning (Al/ML) tools working together to create a digital twin (Figure 2). A digital twin is a digital replica, or "twin," of a physical object or business process. Digital twins can be digital replicas of real components, systems, factories, cities, or even the entire planet. These interdisciplinary simulations drive more EDA growth and require a cost-effective, high-performance infrastructure.

Figure 2. Digital Twin in the Automotive Industry and the use of EDA and CAE

#### **Improved Results**

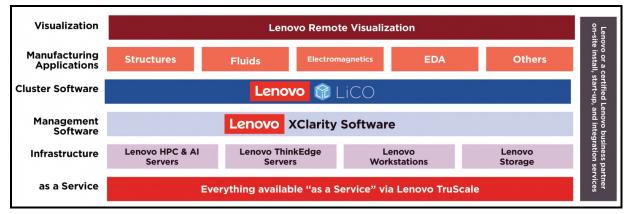

With its technology partnership with AMD, Lenovo provides this flexible, end-to-end, high-performance infrastructure (Figure 3) and increases a manufacturer's ROI from EDA with:

- Accelerated Results: Lenovo systems, powered by AMD EPYC<sup>™</sup> processors, deliver faster time-toresults for EDA tasks, enabling quicker project iterations.

- Enhanced Model Handling: These high-performance systems can manage larger and more complex simulation models, improving simulation accuracy and detail.

- Better Engineering Collaboration: Distributed engineering teams can have the correct information available to the right person at the right time, something hard to do with isolated, individual workstations.

- Energy Efficiency: Lenovo engineers design servers to help reduce power consumption and operational costs by leveraging the energy efficiency of AMD EPYC<sup>™</sup> processors.

- **Reliability and Cost Savings:** Key system characteristics include high reliability, availability, and serviceability, minimizing downtime and helping lower the total cost of ownership.

• Flexible Infrastructure and Integration: Lenovo offers a flexible, pay-as-you-go model with TruScale and seamless integration with immersive manufacturing solutions (Remote Visualization, AR/VR, etc.), optimizing cost management and facilitating better product development throughout the lifecycle.

Figure 3. Lenovo's End-to-End High-Performance Infrastructure for Engineering Simulation

# Read the whitepaper

To learn more about increasing the ROI from your EDA environment, download the new Lenovo whitepaper, "Raising the Bar for High-Performance Manufacturing Solutions", available from:

https://www.lenovo.com/us/en/servers-storage/alliance/amd-hpc/

## Author

Patrick Moakley is the Director of Marketing for HPC & AI at Lenovo Infrastructure Solutions Group. He has over 30 years in IT sales and marketing of x86 systems at Lenovo and IBM and has a Bachelor's degree in Economics from the University of Wisconsin-Madison.

#### Notices

Lenovo may not offer the products, services, or features discussed in this document in all countries. Consult your local Lenovo representative for information on the products and services currently available in your area. Any reference to a Lenovo product, program, or service is not intended to state or imply that only that Lenovo product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any Lenovo intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any other product, program, or service. Lenovo may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

Lenovo (United States), Inc. 8001 Development Drive Morrisville, NC 27560 U.S.A. Attention: Lenovo Director of Licensing

LENOVO PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some jurisdictions do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. Lenovo may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

The products described in this document are not intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change Lenovo product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of Lenovo or third parties. All information contained in this document was obtained in specific environments and is presented as an illustration. The result obtained in other operating environments may vary. Lenovo may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Any references in this publication to non-Lenovo Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this Lenovo product, and use of those Web sites is at your own risk. Any performance data contained herein was determined in a controlled environment. Therefore, the result obtained in other operating environments may vary significantly. Some measurements may have been made on development-level systems and there is no guarantee that these measurements will be the same on generally available systems. Furthermore, some measurements may have been estimated through extrapolation. Actual results may vary. Users of this document should verify the applicable data for their specific environment.

#### © Copyright Lenovo 2025. All rights reserved.

This document, LP1932, was created or updated on April 11, 2024.

Send us your comments in one of the following ways:

- Use the online Contact us review form found at: https://lenovopress.lenovo.com/LP1932

- Send your comments in an e-mail to: comments@lenovopress.com

This document is available online at https://lenovopress.lenovo.com/LP1932.

#### Trademarks

Lenovo and the Lenovo logo are trademarks or registered trademarks of Lenovo in the United States, other countries, or both. A current list of Lenovo trademarks is available on the Web at <a href="https://www.lenovo.com/us/en/legal/copytrade/">https://www.lenovo.com/us/en/legal/copytrade/</a>.

The following terms are trademarks of Lenovo in the United States, other countries, or both: Lenovo®

The following terms are trademarks of other companies:

AMD and AMD EPYC<sup>™</sup> are trademarks of Advanced Micro Devices, Inc.

Other company, product, or service names may be trademarks or service marks of others.