Author

Published

5 Mar 2024Form Number

LP1911PDF size

11 pages, 1.0 MBAbstract

5-level paging is a feature of Microsoft Windows Server 2022 that allows efficient management of massive virtual address spaces, providing support for up to 128 petabytes of virtual memory. This feature is designed to enhance system scalability and address the growing memory requirements of contemporary applications, such as large databases, virtualized environments, and high-performance computing workloads.

This paper introduces the background of the 5-level paging feature and explains how to enable this feature on supported Lenovo ThinkSystem servers. It also shows how to verify the 5-level paging feature is working properly.

5-level paging in Linux: For Linux, see the paper "Introduction to 5-Level Paging in 3rd Gen Intel Xeon Scalable Processors with Linux", available from:

https://lenovopress.lenovo.com/lp1468-introduction-to-5-level-paging

Introduction

Windows operating systems use address-translation support called paging. Paging translates virtual address (aka. Linear address) used by the OS, into physical address, which is used to access memory (or memory mapped I/O).

The Page table is a data structure that the memory manager creates and maintains, and the CPU translates virtual address into physical address. Each page of virtual address space is associated with a system-space structure called a page table entry (PTE), which contains the physical address to which the virtual one is mapped.

4-Level Paging

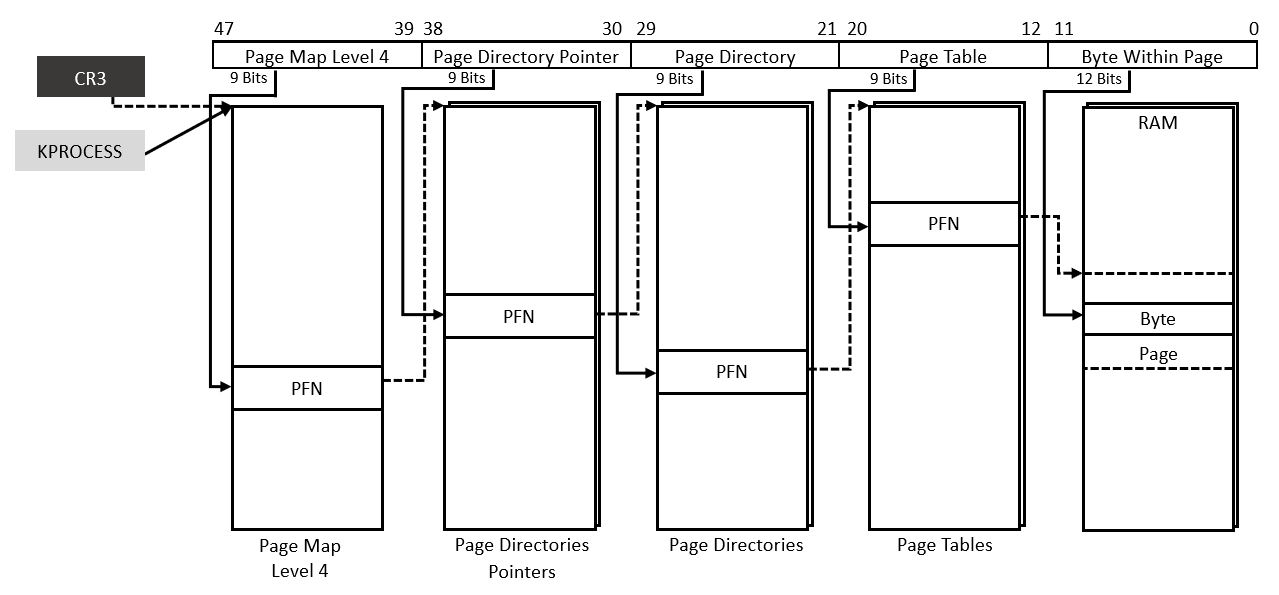

Address translation on x64 architecture is similar to x86, but with a fourth level added which limits virtual address to 48 bits. The components that make up this 48-bit virtual address and the connection between the components for translation purposes are shown in Figure 1.

Figure 1. x64 address translation – 4-Level paging

EXPERIMENT: Viewing the base address of the page table entry (PTE) on 4-level paging by WinDBG

The nt!MiGetPTEaddress routine is part of the Windows NT kernel’s Memory Manager, and it is used to retrieve the address of the PTE corresponding to a given virtual address.

8: kd> uf nt!MiGetPTEaddress

nt!MiGetPteAddress:

fffff801`2febb634 48c1e909 shr rcx,9

fffff801`2febb638 48b8f8ffffff7f000000 mov rax,7FFFFFFFF8h

fffff801`2febb642 4823c8 and rcx,rax

fffff801`2febb645 48b80000000000eaffff mov rax,0FFFFEA0000000000h

fffff801`2febb64f 4803c1 add rax,rcx

fffff801`2febb652 c3 ret

Then, using the kernel debugger !address command to identify virtual memory region of the PTE.

8: kd> !address FFFFEA0000000000

Usage:

Base Address: ffffea00`00000000

End Address: ffffea80`00000000

Region Size: 00000080`00000000

VA Type: PageTables

Hex: ffffea00`00000000

Binary: 11111111 11111111 11101010 00000000 00000000 00000000 00000000 00000000

Bit 63 – No execute

Bit 48~62 – Reserved

Bit 47~12 – PFN

Bit 11 – Write (software)

Bit 10 – prototype (software)

Bit 9 – Copy on write (software)

Bit 8 – Global

Bit 7 – Large page

Bit 6 - Dirty

Bit 5 – Accessed

Bit 4 – Cache disabled

Bit 3 – Write through

Bit 2 - Owner

Bit 1 – Write

Bit 0 - Valid

5-Level Paging

However, with the increasing need for larger address spaces to accommodate complex applications and data structures, a more sophisticated approach became necessary. Introducing 5-level paging, a groundbreaking memory management mechanism introduced in Windows Server 2022.

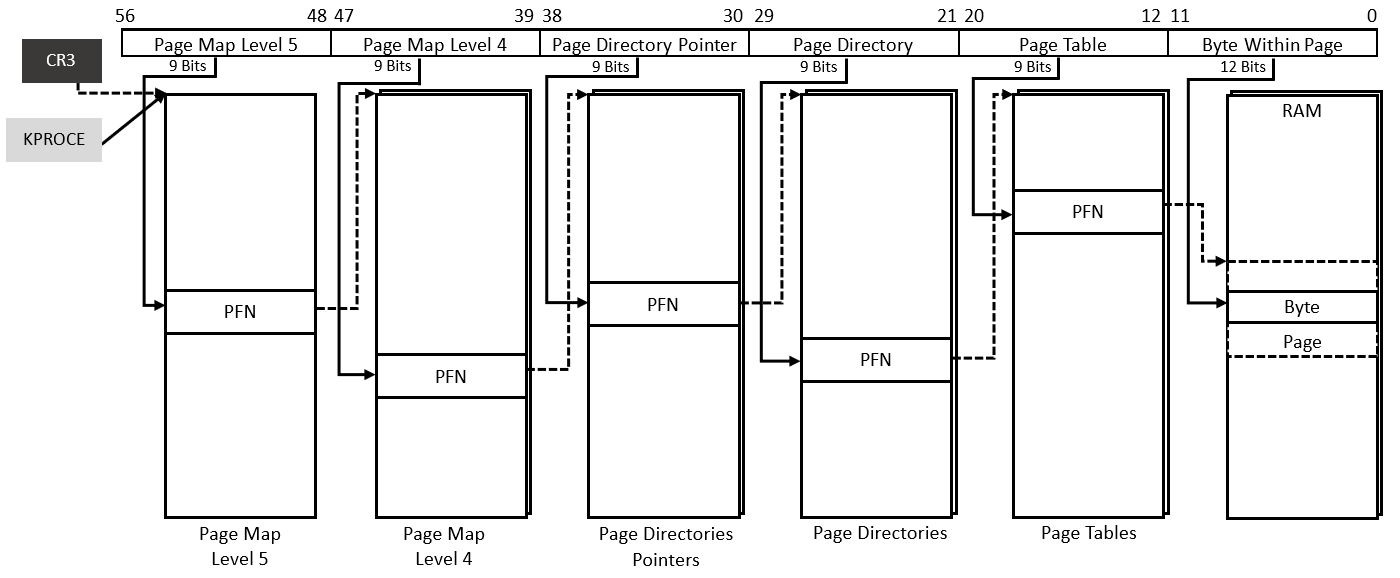

5-level paging is an extension that alleviates the limitation of 57 linear address bits (as depicted in Figure 2). This architectural advancement enables Windows Server 2022 to effectively manage massive virtual address spaces, supporting up to 128 petabytes of virtual memory.

Figure 2. x64 address translation – 5-Level paging

The 5-level paging is designed to enhance system scalability, enabling Windows Server 2022 to meet the escalating memory requirements of contemporary applications, including large databases, virtualized environments, and high-performance computing workloads.

EXPERIMENT: Viewing the base address of the page table entry (PTE) on 5-level paging by WinDBG.

0: kd> uf nt!MiGetPTEaddress

nt!MiGetPteAddress:

fffff803`4a0261c0 48c1e909 shr rcx,9

fffff803`4a0261c4 48b8f8ffffffffff0000 mov rax,0FFFFFFFFFFF8h

fffff803`4a0261ce 4823c8 and rcx,rax

fffff803`4a0261d1 48b80000000000002dff mov rax,0FF2D000000000000h

fffff803`4a0261db 4803c1 add rax,rcx

fffff803`4a0261de c3 ret

0: kd> !address FF2D000000000000

Usage:

Base Address: ff2d0000`00000000

End Address: ff2d0080`00000000

Region Size: 00000080`00000000

VA Type: PageTables

Hex: ff2d0000`00000000

Binary: 11111111 00101101 00000000 00000000 00000000 00000000 00000000 00000000

Bit 63 – No execute

Bit 57~62 – Reserved

Bit 56~12 – PFN (extend from bit 48 to 56 due to PML5)

Bit 11 – Write (software)

Bit 10 – prototype (software)

Bit 9 – Copy on write (software)

Bit 8 – Global

Bit 7 – Large page

Bit 6 - Dirty

Bit 5 – Accessed

Bit 4 – Cache disabled

Bit 3 – Write through

Bit 2 - Owner

Bit 1 – Write

Bit 0 - Valid

We can see the virtual memory address region of the PTE is up to 57 bits virtual address if the 5-level paging is enabled.

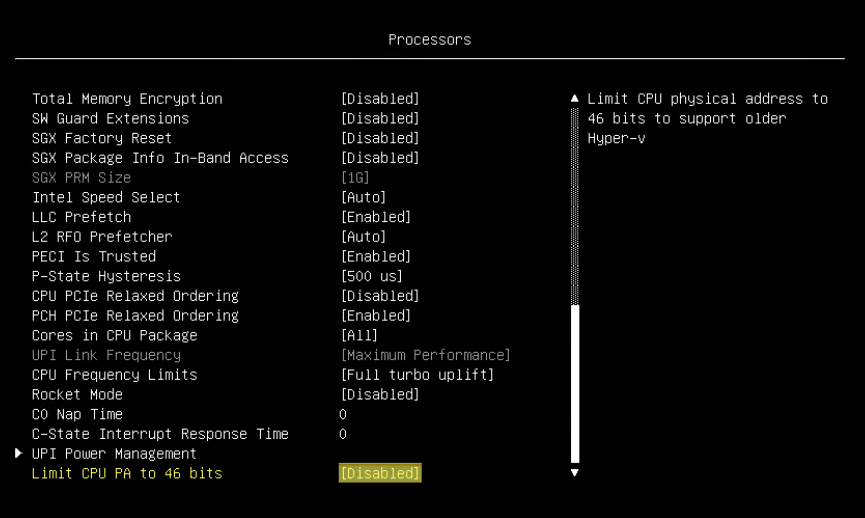

Supported Lenovo servers

To support 5-level paging, servers must have the functionality enabled in UEFI. The following servers all support 5-level paging with Windows Server 2022:

- ThinkSystem V2 with 3rd Gen Intel Xeon Scalable processors

- ThinkSystem SD630 V2

- ThinkSystem SD650 V2

- ThinkSystem SR630 V2

- ThinkSystem SR650 V2

- ThinkSystem V3 with 4th or 5th Gen Intel Xeon Scalable processors

- ThinkSystem SD550 V3

- ThinkSystem SD530 V3

- ThinkSystem SR630 V3

- ThinkSystem SR650 V3

- ThinkSystem ST650 V3

Note: Lenovo ThinkSystem servers with AMD EPYC processors are currently not enabled to support 5-level paging even though the processors support it.

Enabling 5-level Paging in Windows Server 2022

After the UEFI setting is ready for 5-level paging support, you will need to enable a setting in the operating system.

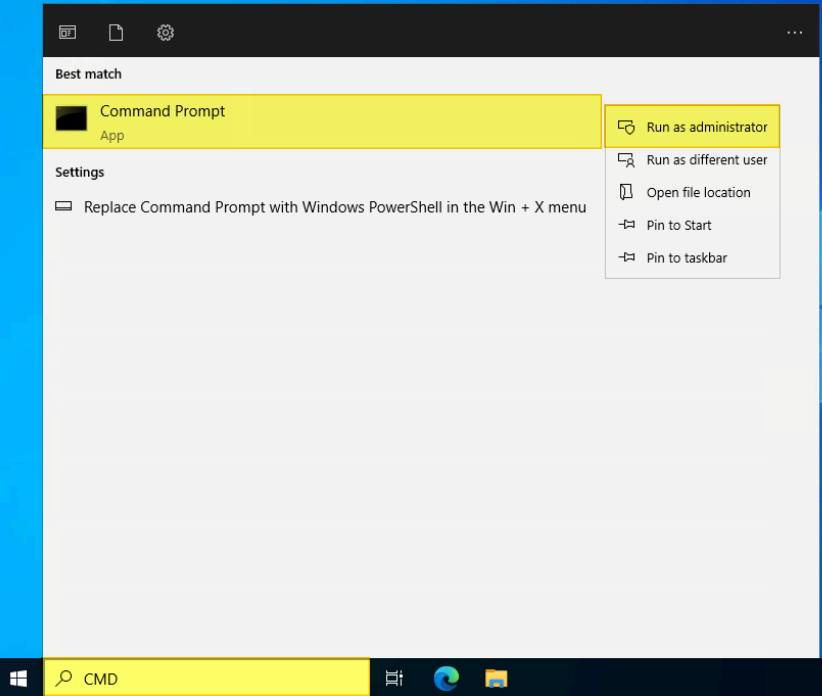

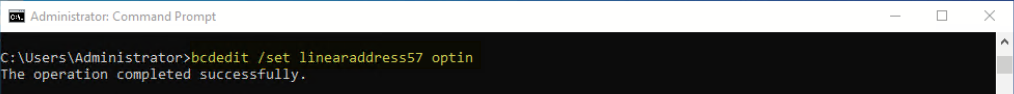

To enable 5-level paging in the BCD store use the following steps:

Checking the status of 5-level paging

To confirm 5-level paging feature is properly configured and running, do the following steps:

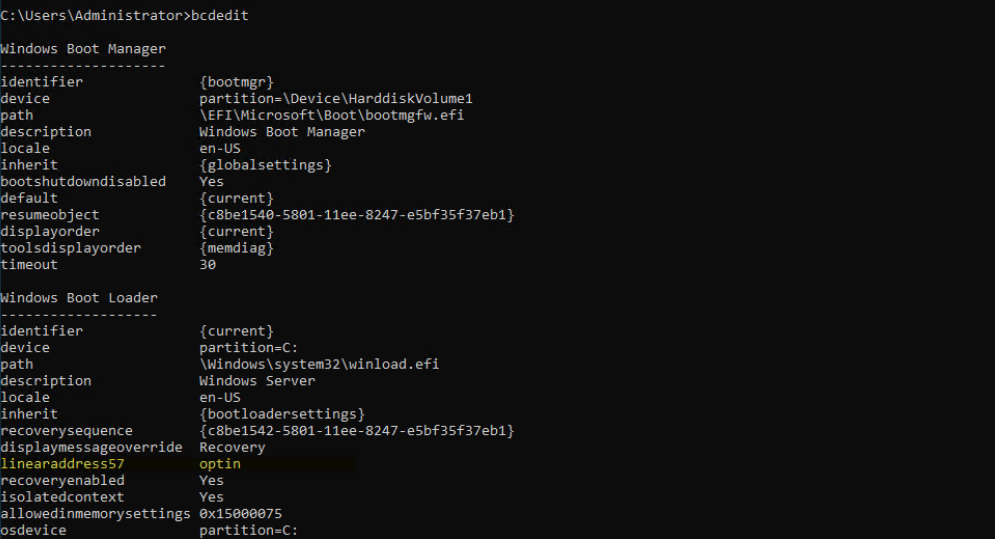

- To confirm LA57 (5-level paging) is enabled, issue bcdedit in a Command Prompt and confirm that linearaddress57 is optin as shown in Figure 6.

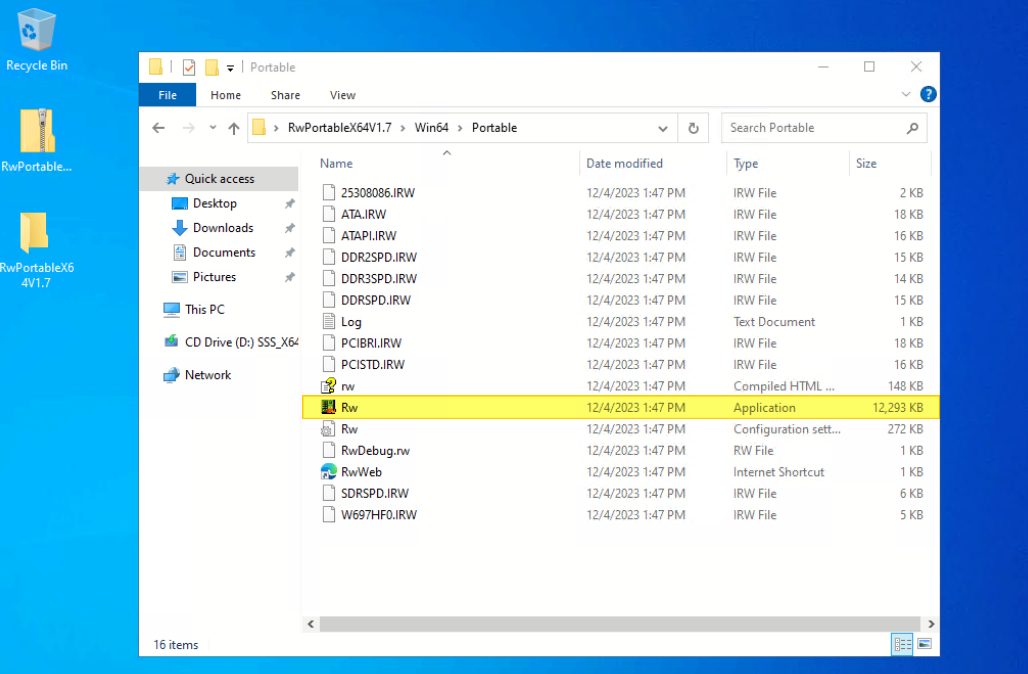

- Processors that support 5-level paging allow software to set an enabling bit, CR4.LA57[bit 12]. If CR4.LA57 = 1, 5-level paging is used. Therefore, to confirm the enabling bit, you will need to download a utility like the RW tool for the confirmation. Download RW tool from:

http://rweverything.com/downloads/RwPortableX64V1.7.zip - Launch the application Rw.exe, Figure 7.

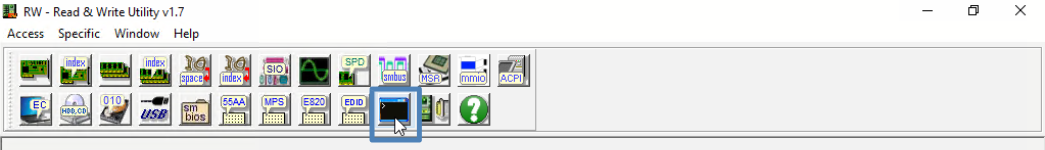

- Click Command as shown in Figure 8.

- Issue rdcr 4 in the Command (as shown in Figure 9), then check if the bit 12 is 1.

References

For more information, see these resources:

- Pavel, Y., Alex I., Mark E. R., & David A. S. (2017). Windows Internals Part1: System architecture, processes, threads, memory management, and more, 7th Washington, United States of America: Microsoft Press.

- Intel White Paper. (2017). 5-Level Paging and 5-Level EPT.

https://www.intel.com/content/www/us/en/content-details/671442/5-level-paging-and-5-level-ept-white-paper.html - AMD64 Architecture Programmer’s Manual Volume 2: System Programming.

https://docs.amd.com/v/u/en-US/24593_3.43

Author

Wewe Chang is a Windows Engineer in the Lenovo Infrastructure Solutions Group, based in Taipei, Taiwan. She has more than 10 years of experience with Windows kernel and user mode debugging.

Special thanks to the following people for their contributions and suggestions:

- Micahel Miller, Advisory Engineer, ThinkAgile Development

- Boyong Li, Senior Engineer, OS Enablement

- Gary Cudak, OS Architect, ThinkAgile Development

- David Watts, Lenovo Press

Trademarks

Lenovo and the Lenovo logo are trademarks or registered trademarks of Lenovo in the United States, other countries, or both. A current list of Lenovo trademarks is available on the Web at https://www.lenovo.com/us/en/legal/copytrade/.

The following terms are trademarks of Lenovo in the United States, other countries, or both:

Lenovo®

ThinkAgile®

ThinkSystem®

The following terms are trademarks of other companies:

AMD and AMD EPYC™ are trademarks of Advanced Micro Devices, Inc.

Intel®, the Intel logo and Xeon® are trademarks of Intel Corporation or its subsidiaries.

Linux® is the trademark of Linus Torvalds in the U.S. and other countries.

Microsoft®, Microsoft Press®, Windows Server®, and Windows® are trademarks of Microsoft Corporation in the United States, other countries, or both.

Other company, product, or service names may be trademarks or service marks of others.

Configure and Buy

Full Change History

Course Detail

Employees Only Content

The content in this document with a is only visible to employees who are logged in. Logon using your Lenovo ITcode and password via Lenovo single-signon (SSO).

The author of the document has determined that this content is classified as Lenovo Internal and should not be normally be made available to people who are not employees or contractors. This includes partners, customers, and competitors. The reasons may vary and you should reach out to the authors of the document for clarification, if needed. Be cautious about sharing this content with others as it may contain sensitive information.

Any visitor to the Lenovo Press web site who is not logged on will not be able to see this employee-only content. This content is excluded from search engine indexes and will not appear in any search results.

For all users, including logged-in employees, this employee-only content does not appear in the PDF version of this document.

This functionality is cookie based. The web site will normally remember your login state between browser sessions, however, if you clear cookies at the end of a session or work in an Incognito/Private browser window, then you will need to log in each time.

If you have any questions about this feature of the Lenovo Press web, please email David Watts at dwatts@lenovo.com.

![Check CR4.LA57 [bit 12] via RW tool](/assets/images/LP1911/Figure9_CheckCR4LA57bit%2012viaRWtool.png)